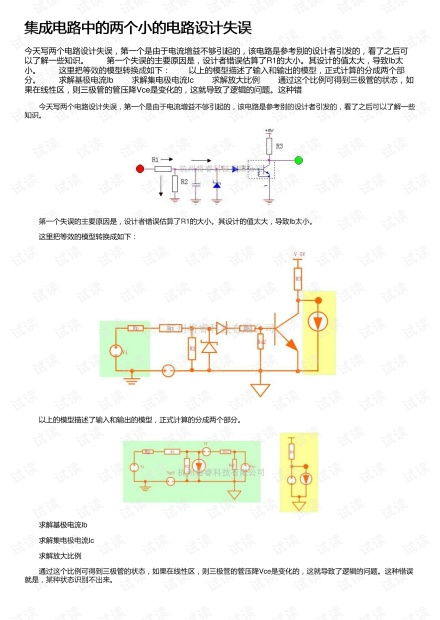

集成电路设计中的两个微小失误 蝴蝶效应与潜在风险

在精密复杂的集成电路(IC)设计领域,一个微小的设计失误可能像蝴蝶效应般引发系统性故障,影响产品性能、可靠性和最终成本。本文将探讨两个常见但易被忽视的小型电路设计失误,分析其产生原因、潜在影响及规避策略。

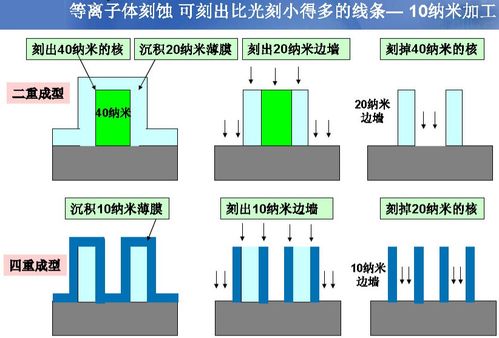

一、信号完整性中的串扰问题

串扰(Crosstalk)是指在相邻导线或电路元件间因电磁耦合而产生的非预期信号干扰。这种失误往往源于布局规划阶段的疏忽,例如未充分考虑高速信号线的间距、屏蔽或布线层分配。

- 产生原因:随着工艺节点不断缩小,导线间距减小、工作频率升高,寄生电容和电感效应加剧。若设计时未对敏感信号线(如时钟线、复位线)采取隔离措施,邻近信号跳变会通过电场或磁场耦合引入噪声。

- 潜在影响:可能导致时序违规、逻辑误判甚至系统崩溃。例如,存储器数据线受干扰可能引发读写错误,而模拟电路中的串扰会降低信噪比。

- 规避策略:采用差分信号布线、增加保护地线、优化层叠结构,并使用电子设计自动化(EDA)工具进行串扰仿真分析。

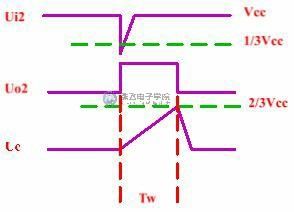

二、电源分配网络(PDN)设计不足

电源分配网络负责为芯片各模块提供稳定电压,但设计中常出现去耦电容配置不当或电源网格阻抗过高等问题。

- 产生原因:设计初期未准确估算不同工作模式下电路的动态电流需求,导致去耦电容容量或布局无法有效抑制电压波动。电源网格的金属宽度和通孔数量不足会增加局部阻抗。

- 潜在影响:引起电源电压骤降(IR Drop)和地弹(Ground Bounce),使晶体管开关速度变慢、噪声容限降低,严重时会导致电路功能失效。

- 规避策略:通过仿真工具建立PDN模型,分层部署去耦电容(包括片上、封装和板级),并采用网格状电源布线以降低阻抗。

集成电路设计中的微小失误常隐藏于细节之中,需通过多轮仿真、验证和团队协作来规避。随着人工智能辅助设计工具的发展,预测性分析正成为预防此类问题的关键手段,但设计师对物理原理的深刻理解始终是不可替代的基石。

如若转载,请注明出处:http://www.gdyuezhi.com/product/18.html

更新时间:2026-04-04 13:23:07