555集成电路的设计原理与应用讲解

555集成电路的设计与讲解

1. 引言

555定时器集成电路(通常简称为555芯片)自1971年由Signetics公司的Hans Camenzind发明以来,已成为电子设计史上最经典、应用最广泛的芯片之一。其设计之精妙、功能之灵活、价格之低廉,使其在模拟与数字电路的交汇处占据了独特地位。本文将系统讲解555集成电路的内部设计原理、工作模式及其经典应用电路。

2. 555集成电路的内部结构与设计原理

555芯片的核心是一个模拟-数字混合电路,其内部设计精巧地集成了模拟比较器、数字逻辑门和功率输出级。

2.1 核心功能模块设计:

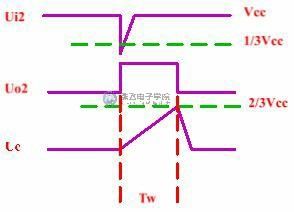

分压网络: 设计使用了三个精密的5kΩ电阻(这也是“555”名称的由来之一),将电源电压(Vcc)等分为三份,分别为两个电压比较器(A1, A2)提供基准电压:

比较器A1(阈值比较器)的“-”端电压为 2/3 Vcc。

- 比较器A2(触发比较器)的“+”端电压为 1/3 Vcc。

- 两个电压比较器: 这是模拟部分的核心。它们将外部引脚(THR阈值和TRG触发)的输入电压与内部基准电压进行比较,输出高低电平,控制后续的数字逻辑。

- SR锁存器: 这是数字逻辑部分的核心。它由两个或非门交叉耦合构成,接收两个比较器的输出信号(R和S),其状态(Q和/Q)决定了最终的输出。这种设计确保了状态的确定性,避免了竞争冒险。

- 放电三极管(Discharge Transistor): 这是一个NPN型三极管,其基极受锁存器的/Q端控制。当/Q为高时,三极管饱和导通,为外部定时电容提供一条对地的低阻放电通路。

- 输出缓冲级: 设计了一个推挽输出级,既能提供较强的拉电流(输出高时),也能提供较强的灌电流(输出低时),驱动能力可达200mA,足以直接驱动LED、小型继电器或扬声器。

2.2 引脚功能设计解析:

1. GND(地): 公共参考点。

2. TRIG(触发): 输入电压低于1/3 Vcc时,触发锁存器置位,输出变高。

3. OUT(输出): 芯片的逻辑状态输出。

4. RESET(复位): 低电平有效的全局复位信号,优先级最高,强制输出低电平。

5. CTRL(控制电压): 允许外部调整两个比较器的基准电压,从而改变定时参数。不用时可接去耦电容到地。

6. THR(阈值): 输入电压高于2/3 Vcc时,触发锁存器复位,输出变低。

7. DIS(放电): 内部放电三极管的集电极开路输出。

8. Vcc(电源): 工作电压范围宽(典型4.5V-16V)。

3. 三种基本工作模式的设计与应用

555的灵活性源于其内部设计支持三种截然不同的工作模式。

3.1 单稳态模式(Monostable)

设计目标: 产生一个精确的、固定宽度的单次脉冲。

电路设计要点: TRIG引脚接外部触发脉冲,THR和DIS引脚相连后,通过一个定时电阻(R)接到Vcc,并通过一个定时电容(C)接地。

工作原理: 触发脉冲(低电平)到来后,输出跳变为高电平,同时放电管关闭,电容C开始通过R充电。当电容电压升至2/3 Vcc时,输出自动跳回低电平,放电管导通,电容迅速放电,等待下一次触发。

脉冲宽度公式: \( T ≈ 1.1RC \)。此模式常用于延时、定时和脉冲整形。

3.2 无稳态模式(Astable)

设计目标: 产生连续不断的方波脉冲,无需外部触发。

电路设计要点: THR和TRIG引脚相连,DIS引脚通过两个电阻(RA, RB)与Vcc和电容C形成充放电回路。

工作原理: 电路在两种状态间自激振荡。电容在R_A+R_B的路径上充电至2/3 Vcc,然后在R_B的路径上通过放电管放电至1/3 Vcc,如此循环。

振荡周期公式: \( T = T{高} + T{低} = 0.693(RA+2RB)C \),占空比始终大于50%。此模式是经典的脉冲发生器、LED闪烁器和音频信号源。

3.3 双稳态模式(Bistable)

设计目标: 作为一个简单的SR锁存器,输出状态由两个输入引脚的电平直接控制。

电路设计要点: 通常不连接外部定时RC网络。TRIG和THR引脚分别作为独立的置位(S)和复位(R)输入端,通过上拉电阻接高电平,用按钮或信号将其拉至低电平来触发。

* 工作原理: 低电平触发TRIG使输出置高,低电平触发THR使输出置低。此模式可用于简单的开关去抖、逻辑控制或记忆单元。

4. 集成电路设计视角下的优势与局限

设计优势:

1. 鲁棒性强: 宽电源电压范围和高抗干扰能力,源于其内部比较器设计和逻辑电平的迟滞特性。

2. 高驱动能力: 输出级设计使其能直接驱动多种负载,简化了系统设计。

3. 极高的性价比: 单一芯片实现了复杂功能,大幅降低了电路成本和设计复杂度。

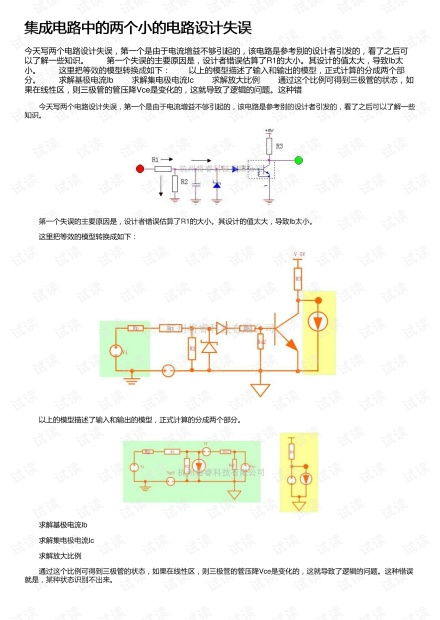

设计局限:

1. 精度与温漂: 定时精度受电阻、电容精度及温度影响,内部比较器的失调电压也会引入误差,不适用于极高精度的定时场合。

2. 功耗: 相比现代CMOS版本(如7555),标准双极型555的静态功耗较高。

3. 频率上限: 受内部器件开关速度限制,最高振荡频率一般在几百kHz量级。

5. 现代演进与设计启示

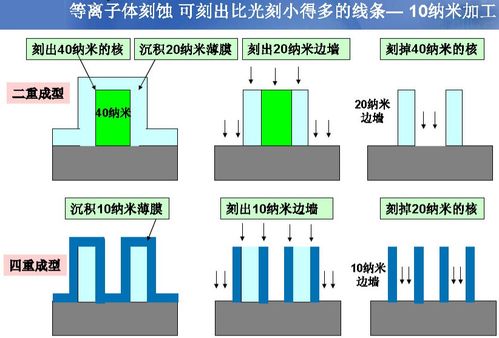

随着半导体工艺的进步,555的设计理念不断演进,出现了CMOS版本的7555/ICM7555,其功耗极低,工作电压更宽;还有双定时器556、四定时器558等集成度更高的变体。

555芯片的设计是“简单实现复杂功能”的典范。它启示工程师:优秀的集成电路设计不仅仅是追求高性能参数,更是要在功能、可靠性、易用性和成本之间找到完美的平衡,从而创造出具有超长生命力和广泛应用场景的“不朽芯片”。时至今日,它仍是学习模拟与数字电路原理、进行原型验证和实现快速开发的绝佳起点。

如若转载,请注明出处:http://www.gdyuezhi.com/product/19.html

更新时间:2026-04-04 22:04:53