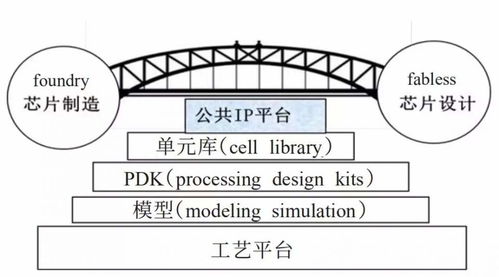

CMOS集成电路设计中电阻的物理层实现方法

在CMOS集成电路设计中,电阻是模拟、混合信号乃至部分数字电路中的基本无源元件。标准CMOS工艺主要针对有源器件(如MOSFET)优化,并未提供像分立元件那样理想的电阻。因此,设计者必须在物理层上巧妙地利用现有的工艺层和结构来实现所需的电阻特性。以下是几种主流的物理层电阻实现方法。

1. 扩散电阻

扩散电阻是利用半导体衬底中掺杂区域的电阻特性实现的。主要包括:

- N+扩散电阻/ P+扩散电阻:利用源/漏区的高浓度掺杂(N+或P+)形成。这类电阻阻值较低(每方块几欧姆到几十欧姆),温度系数和电压系数较差,且与衬底之间存在较大的寄生电容和PN结,适用于对精度和温度特性要求不高的场合,如ESD保护电路中的镇流电阻。

- N阱电阻/ P阱电阻:利用阱区的中等掺杂浓度形成。方块电阻通常为1kΩ/□量级,阻值范围更广,但同样存在较大的寄生电容和电压调制效应。

2. 多晶硅电阻

这是CMOS设计中最常用且性能相对较好的集成电阻。

- 非硅化多晶硅电阻:通过阻挡硅化步骤,保留高电阻率的多晶硅层。方块电阻可达数百欧姆/□,温度系数相对稳定(约1000ppm/℃),线性度好,寄生电容小。是精密电阻(如ADC中的分压电阻、偏置电阻)的首选。

- 硅化多晶硅电阻:经过全硅化工艺,电阻率极低,主要用于制作非常小的导线电阻或接触电阻。

3. 金属电阻

利用互连金属层(如Al、Cu)或其合金制作。

- 优点:线性度极佳,温度系数稳定且可预测,噪声低,与衬底绝缘(寄生电容小)。

- 缺点:方块电阻非常低(通常低于0.1Ω/□),要获得实用阻值(如几百欧姆)需要极其长而细的线条,占用巨大面积,且受工艺最小线宽限制。因此,通常仅用于要求高线性度、低噪声且阻值很小的场合。

4. 有源器件(MOS管)作为电阻

这是一种节省面积且可调的方案,但非线性严重。

- 线性区电阻:将MOS管栅源电压固定,使其工作在深线性区(VDS很小),此时沟道近似为一个受VGS控制的线性电阻。阻值可调,但信号摆幅受限,线性度和温度特性一般。

- 二极管连接方式:将MOS管的栅极和漏极短接,使其始终工作在饱和区,其小信号电阻约为1/gm。常用于有源负载和基准电流源中。

物理设计中的关键考虑因素

- 匹配性:对于差分对、分压器等电路,电阻的匹配性至关重要。设计时应采用共质心、交叉耦合等版图匹配技术,并确保电阻条具有相同的宽度、走向和周围环境。

- 温度系数:不同材料的电阻温度系数差异很大。设计需根据电路的温度稳定性要求选择电阻类型,或采用正负温度系数电阻串联的方式进行补偿。

- 寄生效应:电阻并非理想元件,存在对衬底的寄生电容和(对扩散电阻而言的)寄生PN结二极管。这些寄生参数会影响电路的高频特性,并可能引入电压调制和非线性,在版图布局和电路建模时必须加以考虑。

- 电压系数与线性度:扩散电阻和阱电阻的阻值会随两端电压变化(由于耗尽区宽度调制),线性度差。多晶硅和金属电阻的电压系数则小得多。

- 工艺偏差:绝对阻值受工艺波动影响很大,现代模拟电路设计多依赖于电阻比例而非绝对值。因此,确保相关电阻在版图上紧密相邻并使用相同的材料与宽度,是保证比例精度的关键。

- 噪声:扩散电阻具有较大的1/f噪声和热噪声,而金属电阻的噪声性能最好。在低噪声放大器等电路中需谨慎选择。

###

在CMOS集成电路的物理层实现电阻,是一个在性能、面积、成本和工艺兼容性之间进行权衡的过程。非硅化多晶硅电阻在精度、匹配和寄生效应方面提供了良好的平衡,成为模拟设计的支柱。扩散电阻和阱电阻成本低但性能受限,金属电阻性能优越但面积代价大,而MOS电阻则提供了可调性和紧凑性。成功的电阻设计离不开对工艺特性的深刻理解、精心的版图布局以及对寄生效应的全面建模与验证。

如若转载,请注明出处:http://www.gdyuezhi.com/product/4.html

更新时间:2026-04-20 07:02:33