超大规模集成电路设计中的MOS器件原理(三) 从物理原理到电路设计

在超大规模集成电路(VLSI)的设计中,金属-氧化物-半导体场效应晶体管(MOSFET,简称MOS器件)不仅是构成逻辑门、存储单元和模拟电路的基础砖石,其工作原理更是决定了芯片性能、功耗和可靠性的核心物理机制。本部分作为MOS器件原理探讨的延续,将深入解析其关键特性如何直接映射并深刻影响集成电路的设计实践。

一、MOSFET的静态特性:电路设计的基石

MOSFET的静态特性,主要指其在直流或稳态工作下的电流-电压(I-V)关系,是设计所有数字与模拟电路的根本。

- 工作区域与模型:

- 截止区:当栅源电压(Vgs)低于阈值电压(Vth)时,沟道未形成,漏极电流(Ids)几乎为零。这一特性是数字电路中实现“关断”状态和低静态功耗的关键。在VLSI设计中,精确控制Vth对于降低待机功耗至关重要。

- 线性区(或称三极管区):当Vgs > Vth且Vds较小时,器件像一个由Vgs控制的可变电阻。此区域常用于模拟电路中的电阻设计,以及数字电路中信号传输路径的建模。

- 饱和区:当Vgs > Vth且Vds增大到一定程度(Vds > Vgs - Vth)后,电流Ids基本保持恒定,仅由Vgs控制。这是MOSFET用作放大器和数字反相器驱动级时最主要的工作区域。其平方律特性(Ids ∝ (Vgs - Vth)²)是模拟电路设计的核心方程之一。

在VLSI设计流程中,设计师依赖这些区域的精确数学模型(如BSIM模型)进行电路仿真,以预测性能。

二、MOSFET的动态特性:决定电路速度与功耗

动态特性关乎器件对快速变化信号的响应能力,直接决定了集成电路的工作频率和动态功耗。

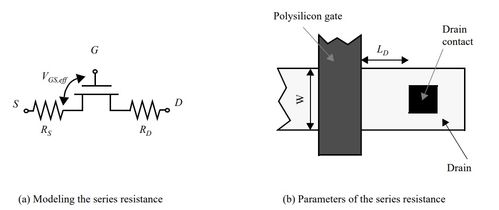

- 寄生电容效应:MOSFET内部存在多种寄生电容,如栅氧化层电容(Cox)、覆盖电容、结电容等。这些电容的充放电过程:

- 限制速度:构成了电路延时(如反相器的传播延时)的主要部分。VLSI设计中,优化晶体管尺寸(W/L)以平衡驱动电流和负载电容,是提升速度的常用手段。

- 产生动态功耗:在数字电路开关过程中,对寄生电容进行充放电所消耗的能量(P_dynamic ∝ C Vdd² f),是芯片动态功耗的主要来源。降低工作电压(Vdd)是减少此类功耗最有效的途径。

- 沟道长度调制效应:在饱和区,有效沟道长度随Vds增大而略微缩短,导致Ids随Vds缓慢增加。这影响了理想电流源的输出阻抗,在模拟电路(如电流镜、运放)设计中必须仔细考虑,以获取高增益。

三、短沟道效应与现代VLSI设计的挑战

随着工艺节点进入纳米尺度,传统的长沟道MOSFET理论需要重大修正,短沟道效应成为主导设计约束的核心问题。

- 阈值电压滚降(Vth Roll-off):沟道变短后,栅极对沟道的控制力减弱,源/漏耗尽区的影响增大,导致Vth随沟道长度减小而下降。这使得器件关断特性变差,亚阈值漏电流增大,严重增加了静态功耗。VLSI设计必须采用更复杂的功耗管理技术,如电源门控和多阈值电压库。

- 漏致势垒降低(DIBL):高漏极电压会进一步降低源端的势垒,使Vth随Vds升高而降低,加剧关态漏电,并导致输出阻抗降低。

- 迁移率退化与速度饱和:高电场下,载流子迁移率下降,速度趋于饱和,使得Ids与Vgs的关系从平方律变为近似线性关系。这影响了电路的驱动能力模型。

- 热载流子效应与可靠性:高电场下产生的高能载流子可能注入栅氧层,造成器件性能的渐进性退化,影响芯片寿命。设计时必须进行严格的可靠性仿真与验证。

四、从器件到系统:设计考量

理解MOS器件原理最终是为了指导系统级设计:

- 性能-功耗-面积(PPA)权衡:晶体管的尺寸(W/L)、阈值电压(Vth)和氧化层厚度(Tox)等参数,是设计师在PPA之间进行权衡的直接“旋钮”。例如,采用高Vth器件降低漏电但牺牲速度,或采用宽晶体管提高驱动能力但增加面积和电容。

- 工艺角(Corner)分析与变异:制造过程中的工艺波动会导致MOS器件参数(如Vth, Cox)发生变化。VLSI设计必须在“快-快”、“慢-慢”、“典型”等多种工艺角以及温度、电压(PVT)条件下进行仿真,确保电路在所有情况下功能正确、性能达标。这直接源于器件参数对环境的敏感性。

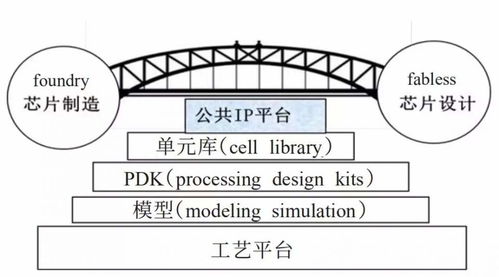

- 新型器件与电路技术:为了应对短沟道效应的挑战,现代VLSI设计已广泛采用应变硅技术、高K金属栅(HKMG)、FinFET(鳍式场效应晶体管)乃至GAA(环栅晶体管)等新型器件结构。这些技术的核心原理都是为了在纳米尺度下恢复栅极对沟道的控制力,降低漏电,其设计模型和方法学也随之演进。

结论

MOS器件原理是连接半导体物理与超大规模集成电路设计的桥梁。从静态的I-V方程到动态的电容效应,从经典的长沟道理论到纳米尺度的短沟道效应,对器件行为的深刻理解,是设计师进行电路创新、性能优化和解决功耗、可靠性等核心挑战的先决条件。在摩尔定律持续推进的今天,器件原理与电路设计的协同创新,比以往任何时候都更加紧密和关键。

如若转载,请注明出处:http://www.gdyuezhi.com/product/5.html

更新时间:2026-04-20 04:02:37